# Hybrid System

# HS 9410 Series 8 Channel, 12-Bit Data Acquisition System with µP Interface

# **FEATURES**

- Complete 8 Channel, 12-bit Data Acquisition System with MUX, S/H, REF, Clock and threestate outputs

- Full 8- or 16-Bit Microprocessor Bus Interface

- Guaranteed Linearity Over Temperature

- High Throughput Rate: 25kHz

- Hermetic 28-Pin Ceramic or Low Cost Epoxy

- Low Power: 600mW

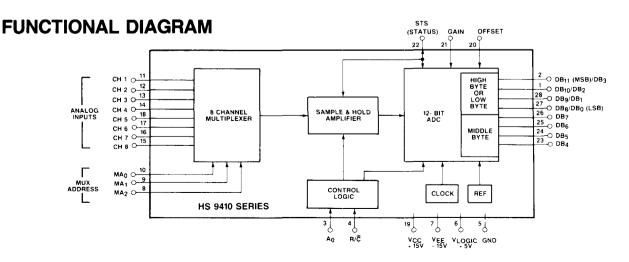

The HS 9410 Series is a complete 8 channel, microprocessor compatible, 12-Bit data acquisition system with all the interface logic to connect directly to 8- or 16-Bit microprocessor buses. It is contained in a 28-pin DIP and includes an 8 channel multiplexer, a sampleand-hold amplifier, and a 12-Bit A/D converter along with the control logic needed to perform a complete data acquisition function. System throughout rate is 25 kHz for full rated accuracy.

The Analog-to-Digital converter section contains the now standard HS 574 12-Bit ADC. This ADC is implemented with advanced bipolar and CMOS LSI chips resulting in maximum performance at lowest cost. The SAR, 12-Bit decoded D/A, control logic, switches and buffers are fabricated using CMOS processing for lowest power. A unique comparator, reference and required amplifiers are fabricated using linear bipolar processes for maximum speed and reduced offset and drift over temperature.

Incorporating a unique precision comparator design, the ADC offers several advantages over more conventional circuits. A proprietary decoded 12-Bit D/A provides in-

creased accuracy, lower drift and reduced output noise over the A/D operating range. Precision low TCR laser trimmed resistors are used in the converter for setting critical performance parameters including gain, offset, input ranges, and accuracy.

The HS 9410 Series is offered in a hermetically-sealed package for use over a wide temperature range and for MIL-STD-883 requirements. Hybrid Systems' proprietary commercial package is offered for applications not requiring the wider temperature exposure.

The HS 9410 Series operates from  $\pm 15V^*$  and  $\pm 5V$  with a total power consumption of 600 mW. To take advantage of the 28-pin package the user must specify an input range of 0 to  $\pm 10V$ ,  $\pm 5V$  or  $\pm 10V$  when ordering. Four basic product grades are available; J and K models are specified over a temperature range of 0°C to +70°C while the S and T models are specified over an extended temperature range of -55 °C to +125 °C. Full screening to MIL-STD-883 Rev. C, Level B and processing in accordance with Method 5008.1 is available with models specified as "B."

\* ± 12V operation possible; consult factory for further information.

# **SPECIFICATIONS**

(Typical  $@+25^{\circ}C$  with  $V_{CC} = +15V$ ,  $V_{EE} = -15V$ ,  $V_{LOGIC} = +5V$ , unless otherwise specified.)

| MODEL                                                         | HS 941XJ                                                               | HS 941XK     | HS 941XS           | HS 941XT          |

|---------------------------------------------------------------|------------------------------------------------------------------------|--------------|--------------------|-------------------|

| TRANSFER CHARACTERISTICS                                      |                                                                        |              |                    |                   |

| Resolution                                                    | 12-Bits                                                                | •            | £                  |                   |

| Number of Channels                                            | 8 Single-Ended                                                         |              |                    | •                 |

| Throughput Rate                                               | 25 kHz                                                                 | •            | -                  |                   |

| ANALOG INPUTS                                                 |                                                                        |              |                    |                   |

| Input Ranges <sup>1</sup> (Specified as a suffix in the moi   |                                                                        |              | ń                  |                   |

| HS 9410<br>HS 9411                                            | 0 to +10V<br>±5V                                                       | *            | *                  |                   |

| HS 9412                                                       | ± 10V                                                                  | *            | *                  | *                 |

| Input Bias Current per Channel                                |                                                                        |              |                    |                   |

| I <sub>IB</sub> 25°C                                          | ± 1.0nA                                                                | •            | ± 250nA max        |                   |

| -55°C to +125°C<br>Input Impedance                            |                                                                        |              | ± 230HA HIAX       |                   |

| ON Channel                                                    | 10 <sup>10</sup> QII 100pf                                             | *            | n                  |                   |

| OFF Channel                                                   | 10 <sup>10</sup> $\Omega$ II 10pf                                      | •            | •                  | *                 |

| DIGITAL INPUTS                                                |                                                                        |              |                    |                   |

| Logic Inputs                                                  |                                                                        |              |                    |                   |

| R/C. A <sub>o</sub>                                           | 0.007                                                                  |              | *                  |                   |

| V <sub>IH</sub> min<br>V <sub>IH</sub> max                    | + 2.0V ·<br>+ 5.5V                                                     |              | •                  | *                 |

| V <sub>IL</sub> max                                           | +0.8V                                                                  | *            | +                  | *                 |

| V <sub>IL</sub> min                                           | - 0.5V                                                                 | •            |                    | *                 |

| I <sub>IL</sub> max                                           | ± 50µA max                                                             | *            | *                  | *                 |

| I <sub>IH</sub> max<br>Multiplexer Inputs                     | ± 50µA max                                                             | •            |                    |                   |

| V <sub>II</sub> max                                           | + 0.8V                                                                 | •            |                    | • _               |

| V <sub>IH</sub> min                                           | + 2.4V                                                                 | •            | +4.0V <sup>2</sup> | $+4.0V^{2}$       |

| Input Capacitance (All Digital Inputs)                        | 5pF typ                                                                | *            | *                  | •                 |

| Minimum Start Pulse R/C-Negative                              | 150ns                                                                  |              | w .                |                   |

| -                                                             | 133,13                                                                 |              |                    |                   |

| SIGNAL DYNAMICS                                               |                                                                        |              |                    |                   |

| Conversion Time<br>12-Bit Conversion                          | 30µs max                                                               | •            | *                  | •                 |

| 8-Bit Conversion                                              | 21µs max                                                               | *            | R.                 | *                 |

| DIGITAL OUTPUTS                                               | ,                                                                      |              |                    |                   |

| Logic Outputs                                                 |                                                                        |              |                    |                   |

| DB <sub>11</sub> -DB <sub>0</sub> STS                         |                                                                        | v            |                    |                   |

| Logic 0                                                       | +0.4V max, I <sub>OL</sub> ≤1.6mA                                      | •            | *                  |                   |

| Logic 1                                                       | +2.4V min, 1 <sub>OH</sub> ≤0.5mA                                      | *            | **                 | •                 |

| Leakage (High Z State)<br>Capacitance                         | ± 40µA typ (DB <sub>11</sub> -DB <sub>0</sub> only)<br>5pF             | *            | ń                  | •                 |

| Output Code Configuration                                     | 92.                                                                    |              |                    |                   |

| Unipolar                                                      | Positive True Binary                                                   | •            | •                  | *                 |

| Bipolar                                                       | Positive True Offset Binary                                            | •            | ,                  | •                 |

| POWER SUPPLY                                                  |                                                                        |              |                    |                   |

| VLOGIC                                                        | + 4.5 to + 5.5 Volts @ 20mA max                                        | •            | *<br>•             | •                 |

| vCC                                                           | + 13.5 to + 16.5 Volts @ 25mA max<br>- 13.5 to - 16.5 Volts @ 35mA max | *            | ,                  | *                 |

| VEE<br>Power Dissipation                                      | 800mW typ, 1.1W max                                                    | *            | 600mW typ, 1W max  | 600mW typ, 1W max |

| Rejection <sup>3</sup>                                        | 0.00006/04 hap 0.00504/06 may                                          |              | •                  |                   |

| VLOGIC                                                        | 0.002%/% typ, 0.005%/% max<br>0.002%/% typ, 0.005%/% max               | •            | <b>*</b>           |                   |

| V <sub>CC</sub><br>V <sub>EE</sub>                            | 0.002%/% typ, 0.005%/% max                                             |              | •                  | *                 |

| ACCURACY                                                      | <b>,</b> .                                                             |              |                    |                   |

| Linearity Error (% of F.S.R. max)                             | ± 0.025                                                                | ± 0.012      | ± 0.025            | ±0.012            |

| Offset 4                                                      |                                                                        | •            | _                  | -                 |

| Unipolar (% of F.S.R. max)                                    | ± 0.05                                                                 |              | ± 0.25             | ± 0.1             |

| Bipolar (% of F.S.R. max) Gain <sup>4</sup> (% to F.S.R. max) | ± 0.25<br>± 0.3                                                        | ± 0.1        | ±0.25              | ± 0.1             |

| STABILITY                                                     | 10.0                                                                   |              |                    |                   |

| ····                                                          | .06                                                                    | , 0 ¢        | . 25               | ±2.5              |

| Linearity (ppm/°C max) Unipolar Offset (ppm/°C max)           | ± 0.5<br>± 10                                                          | ± 0.5<br>± 5 | ± 2.5<br>± 25      | ± 2.5<br>± 20     |

| Bipolar Offset (ppm/°C max)                                   | ± 25                                                                   | ± 20         | ± 25               | ± 20              |

| Gain (Scale Factor)(ppm/°C max)                               | ±50                                                                    | ± 20         | ± 50               | ± 25              |

| TEMPERATURE RANGE                                             |                                                                        | ·····        |                    |                   |

| Operating                                                     | 0° to +70°C                                                            | *            | - 55°C to + 125°C  | -55°C to +125°C   |

| Storage                                                       | - 25°C to + 85°C                                                       |              | 65°C to +150°C     | -55°C to +125°C   |

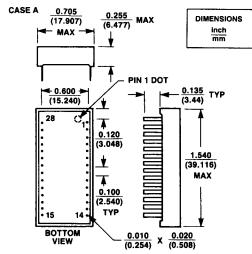

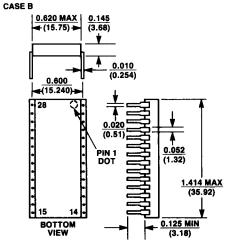

| PACKAGE                                                       | CASE A                                                                 | CASE A       | CASE B             | CASE B            |

NOTES:

1. For J and K models, positive analog input voltage should not exceed V<sub>CC</sub> = 4 volts. Exceeding V<sub>CC</sub> = 4 volts can cause an OFF channel to be turned ON. Negative input voltages and input voltages for S and T models may go to supply voltages. Input voltages exceeding these values will not result in permanent damage as long as the absolute maximum ratings are not exceeded.

2. 1K pullup to +5V recommended for MA<sub>0</sub>-MA<sub>2</sub> when driven by TTL.

3. Maximum change over rated supply voltage.

4. Externally adjustable to zero. See Applications Information.

<sup>\*</sup>Specifications same as HS 9410J

#### **PACKAGE OUTLINE**

Dimensions shown in inches and (mm).

# **PIN ASSIGNMENTS**

| PIN | FUNCTION                               | PIN | FUNCTION                         |

|-----|----------------------------------------|-----|----------------------------------|

| 1   | DB <sub>10</sub> /DB <sub>2</sub>      | 28  | DB <sub>9</sub> /DB <sub>1</sub> |

| 2   | DB <sub>11</sub> (MSB)/DB <sub>3</sub> | 27  | DB <sub>8</sub> /DB <sub>0</sub> |

| 3   | $A_{o}$                                | 26  | DB <sub>7</sub>                  |

| 4   | R/C                                    | 25  | DB <sub>6</sub>                  |

| 5   | GROUND                                 | 24  | DB <sub>5</sub>                  |

| 6   | V <sub>LOGIC</sub>                     | 23  | DB <sub>4</sub>                  |

| 7   | V <sub>EE</sub>                        | 22  | STS(STATUS)                      |

| 8   | MUX ADDRESS A <sub>2</sub>             | 21  | GAIN                             |

| 9   | MUX ADDRESS A <sub>1</sub>             | 20  | OFFSET                           |

| 10  | MUX ADDRESS A <sub>o</sub>             | 19  | V <sub>cc</sub>                  |

| 11  | INPUT CH 1                             | 18  | INPUT CH 5                       |

| 12  | INPUT CH 2                             | 17  | INPUT CH 6                       |

| 13  | INPUT CH 3                             | 16  | INPUT CH 7                       |

| 14  | INPUT CH 4                             | 15  | INPUT CH 8                       |

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>cc</sub> to Common GND 0 to + 16.5V |

|--------------------------------------------|

| V <sub>EE</sub> to Common GND 0 to - 16.5V |

| $V_{LOGIC}$ to Common GND 0 to +7V         |

| Control Inputs (A <sub>o</sub> , R/C) to   |

| Common GND $-0.5$ V to $V_{LOGIC} + 0.5$ V |

| Power Dissipation                          |

| Lead Temperature, Soldering 300 °C, 10Sec  |

| Maximum Input Voltage                      |

| Minimum Input Voltage                      |

| Analog Input Maximum Current               |

#### **CONTROL FUNCTIONS**

The HS 9410 Series contains control functions necessary to provide for microprocessor interface. All control functions are defined in Tables 1, 2, and 3.

| Function                           | Definition             | Function                                                                                                                                                                                                                                                            |

|------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/C                                | Read/Convert           | <ol> <li>1. Linitiates conversion.</li> <li>2. Low (0) disconnects data bus.</li> <li>3. High (1) initiates read.</li> </ol>                                                                                                                                        |

| A <sub>0</sub>                     | Device Address         | <ol> <li>Selects conversion mode.</li> <li>12-bits if low (0), 8-bits if high (1) when R/C  L.</li> <li>In read mode A₀ selects the output format. If low (0) then 8 MSB's (high and middle byte) or if high (1) then only low byte and trailing zeroes.</li> </ol> |

| MA <sub>0</sub>                    |                        |                                                                                                                                                                                                                                                                     |

| MA <sub>1</sub><br>MA <sub>2</sub> | Multiplexer<br>Address | Select Channels 1-8<br>(see MUX Logic Table 3)                                                                                                                                                                                                                      |

Table 1. Defining the Control Functions

| Contr | oi Inputs      | Operation                                       |  |

|-------|----------------|-------------------------------------------------|--|

| R/C   | A <sub>0</sub> | · ·                                             |  |

| Ĩ.    | 0              | Initiates 12-bit conversion                     |  |

| Ł     | 1              | Initiates 8-bit conversion                      |  |

| 1     | 0              | Enables 8 MSB's (high byte)                     |  |

| 1     | 1              | Enables 4 LSB's (low byte) and 4 trailing zeros |  |

| 0     | Х              | Output data (DB) goes to high impedance state.  |  |

Table 2. Truth Table - Control Inputs

| Mux Address<br>Inputs |                | Channel<br>Selected | NOTES:  1. 1 indicates logic HIGH.  2. 0 indicates logic LOW. |                                                                                |  |

|-----------------------|----------------|---------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| A <sub>2</sub>        | A <sub>1</sub> | A <sub>0</sub>      |                                                               | X indicates don't care.                                                        |  |

| 0                     | 0              | 0                   | 1                                                             | <ol> <li>indicates operation commend<br/>on high to low transition.</li> </ol> |  |

| 0                     | 0              | 1                   | 2                                                             | 5. MSB → XXXX XXXX                                                             |  |

| 0                     | 1              | 0                   | 3                                                             | High Middle<br>Byte Byte                                                       |  |

| 0                     | 1              | 1                   | 4                                                             | 6. <u>XXXX</u> ← LSB                                                           |  |

| 1                     | 0              | 0                   | 5                                                             | Low<br>Byte                                                                    |  |

| 1                     | 0              | 1                   | 6                                                             | 3,16                                                                           |  |

| 1                     | 1              | 0                   | 7                                                             |                                                                                |  |

| 1                     | 1              | 1                   | B                                                             |                                                                                |  |

Table 3. Truth Table - Multiplexer Address

# APPLICATIONS INFORMATION

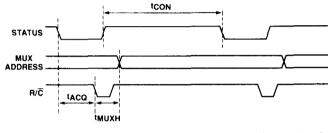

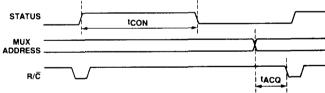

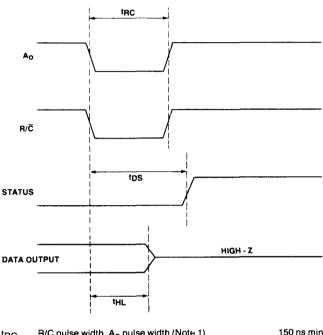

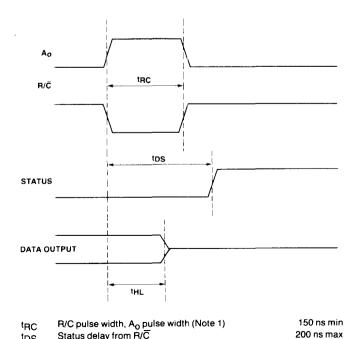

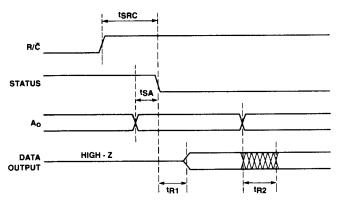

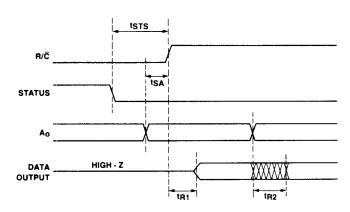

The timing diagrams are shown in Figures 1 through 6. Figures 1 and 2 show how the multiplexer addressing is related to the convert cycle, while Figures 3 and 4 show the timing sequence to start either a 12- or an 8-bit conversion. Figures 5 and 6 show how to read the multiplexed data from the internal register in the HS 9410.

#### Figures 1 and 2

The multiplexer address can be changed either during or after a conversion, but care must be taken not to change the address within 1 microsecond after the convert command to insure that the sample/hold will not start to acquire the signal of the new channel. After the multiplexer address has been changed, you must allow the sample/hold at least 10 microseconds in sample mode to acquire the new input signal.

t<sub>MUXH</sub> Multiplexer address hold time after convert command 1<sub>us</sub> min Minimum time between conversions (S/H acquisition time) 10µs min Conversion time for -12 bit resolution J,K-Models 30µs max S.T-Models 30us max - 8 bit resolution J,K-Models 22us max S,T-Models 22µs max

Figure 1. Timing Diagram 8/12-Bit Conversion, MUX Address Changes During Conversion

Minimum time between MUX address change <sup>t</sup>ACQ 10µs min and convert command Conversion time - Specifications, see Figure 1

Figure 2. Timing Diagram 8/12-Bit Conversion, MUX Address Changes Between Conversions

#### Figures 3 and 4

Figures 3 and 4 show how to start a convert cycle. The logic level of the A<sub>O</sub> line determines whether a 12- or 8-bit conversion will be initiated. If Ao is low during the start convert command, a 12 bit conversion will be started; if Ao is high, an 8-bit conversion will occur. The Ao line has to be setup when the R/C line goes to logic '0' and must remain in the desired level for at least 150 ns. The R/C line is used both to start a conversion and to read the output data. If R/C is going low a conversion is initiated. This is indicated by the STATUS line going high. A second start convert command during a conversion will be ignored. The R/C pulse must have a minimum width of 150 ns. For optimum performance the rising edge of the R/C pulse should not occur during a conversion if the conversion has been in progress for more than 1.5 microseconds, i.e., the negative R/C pulse should be either shorter than 1.5 microseconds or longer than the conversion time.

R/C pulse width, Ao pulse width (Note 1) tRC Status delay from R/C 200 ns max tDS 150 ns max Output float delay

Figure 3. Timing Diagram to Start a 12-Bit Conversion

Figure 4. Timing Diagram to Start an 8-Bit Conversion

Output float delay

150 ns max

tos

tHI

### Figures 5 and 6

If a conversion is in progress the data output lines are disabled and in the high-impedance state. Data can be enabled by bringing the R/C line high after a conversion is complete (this is indicated by the STATUS line going low; Fig. 6). If R/C has been returned high during a conversion the data outputs will be enabled automatically after STATUS goes low (Fig. 5). The Ao line is used to address either the 8 upper data bits or the 4 lower data bits followed by 4 trailing zeros. If an 8-bit conversion has been performed the lower 4 bits will always be '0'. After an 8-bit conversion, it is not necessary to read the lower 4 bits prior to starting a new conversion. Note that Ao only controls the address of the two data bytes while the high impedance state of the output buffers is controlled by the R/C and STATUS line. The output buffers will not return to the high impedance state when Ao is changed to address the second data byte.

Figure 5. Timing Diagram Read Cycle, R/C Going High During Conversion

#### NOTES:

- 1. For optimum performance the positive edge of the  $R/\overline{C}$  pulse should not occur during a conversion if the conversion has been started for more than 1.5 microseconds. The negative  $R/\overline{C}$  pulse should be either shorter than 1.5 microseconds or longer than the conversion time.

- 2. If the set-up time for  $A_0$  cannot be met, the access time for the first data byte will be increased. In that case the first data byte will become valid 225 ns max after the change of the  $A_0$  line.

tsts Status going low prior to R/C going high 0 ns min

tsA Ao set-up time prior to R/C going high (Note 2) 100 ns min

tsA Access time, 1st data byte (from R/C) 125 ns max

ts2 Access time, 2nd data byte (from Ao) 225 ns max

Figure 6. Timing Diagram Read Cycle, R/C Going High After Conversion

## USING THE AO LINE

The state of  $A_o$  at the start of a conversion places the DAS in either a full 12-bit conversion or in an 8-bit 'short cycle' mode. During a READ at the end of a conversion  $A_o$  is used to format the data as follows:

| MODE                                              |

|---------------------------------------------------|

| Short cycle 8-bit conversion                      |

| Full 12-bit conversion                            |

|                                                   |

| Data = Low Byte (LSB)                             |

| followed by zeros                                 |

| Data = High Byte (MSB's) followed by middle byte. |

| followed by middle byte.                          |

|                                                   |

In a  $\mu$ P application A<sub>o</sub> can be considered a pair of  $\overline{\text{W/R}}$  locations as follows:

#### 1. Prior to Conversion (WRITE)

$\overline{W/R} = 1$  in high address (A<sub>o</sub> = 1)  $\overline{W/R} = 1$  in low address (A<sub>o</sub> = 0) LSB's & zeros 8 MSB's only

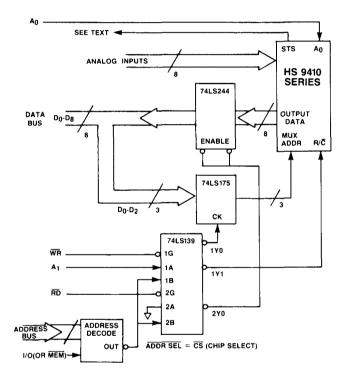

#### **MICROPROCESSOR INTERFACE**

The HS 9410 Series DAS can be interfaced with most popular 8-bit microprocessors. The DAS may be either positioned in a memory location (memory map) or as an I/O device. In the case of memory mapping, the DAS acts as a static RAM where READ and WRITE instructions are given to the selected address. When the DAS is connected as an I/O device, the I/O enable can be substituted for the MEMR or MEMW command. Figure 7 shows a typical scheme to implement this interface.

STS is not used in this example; the uP must read data 30 us after conversion starts. This delay can be generated with NOP or other instructions inserted between the WRITE and READ functions. The STS line can also be used to cause the processor to WAIT or HALT or can be used as an interrupt line such as IREQ (in the case of 6800 or 6502).

|                  |                |          |    |          | HS 9410 Function |                     |  |

|------------------|----------------|----------|----|----------|------------------|---------------------|--|

| $\mathbf{A}_{0}$ | A <sub>1</sub> | WR       | RD | ADDR SEL | Read/Write       | Operation           |  |

| X                | 0              | LF       | 1  | 0        | WRITE            | MUX ADDRESS         |  |

| 0                | 1              | ¥        | 1  | 0        | WRITE            | START 12-BIT CONV.  |  |

| 1                | 1              | <b>T</b> | 1  | 0        | WRITE            | START 8-BIT CONV.   |  |

| 0                | х              | 1        | 0  | 0        | READ             | HIGH BYTE (8 MSB's) |  |

| 1                | х              | 1        | 0  | 0        | READ             | LOW BYTE (4 LSB's)  |  |

#### NOTES:

- 1. 1 indicates logic HIGH. 2. 0 indicates logic LOW. 3. X indicates don't care.

- ▲ indicates operation commences on low to high transition 5. indicates operation commences on high to low transition

- Figure 7. Interfacing the HS 9410 Series

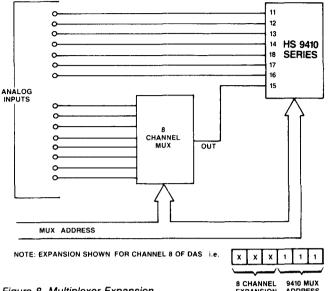

#### **INPUT EXPANSION**

The DAS is configured with an 8 channel high level multiplexer input. This was done to optimize package size (28 pin DIP) and cost. In the event the user wishes to increase the number of input channels, a double rank MUX input is recommended (series connected). This typical configuration is shown in Figure 8.

Figure 8. Multiplexer Expansion

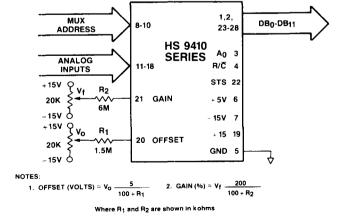

#### ZERO AND GAIN CONNECTIONS

The DAS is normally used with external zero and gain calibration potentiometers. However, if maximum accuracy is not required, they may be omitted. The zero control has a range of about ±20LSB, and the gain control has a range of about ± 13LSB.

Proper gain and zero calibration requires great care and the use of extremely sensitive and accurate instruments. The voltage source used as a signal input must be very stable. It also should be capable of being set to within 1/10LSB at both ends of its range.

The DAS's zero and gain adjustments are independent of each other if the zero (or offset) adjustment is made first.

Figure 9. Gain and Offset Input Connections

#### **ZERO ADJUSTMENT PROCEDURE**

- 1. For unipolar ranges:

- a) Set input voltage precisely to + 1/2 LSB.

- b) Adjust zero control until converter is switching from 000000000000 to 00000000001.

- 2. For bipolar ranges:

- a) Set input voltage precisely to ½LSB above F.S.

- b) Adjust zero control until converter is switching from 000000000000 to 000000000001

#### **GAIN ADJUSTMENT PROCEDURE**

- 1. Set input voltage precisely to ½LSB less than 'all bits on' value. Note that this is 1½LSB less than nominal full scale.

- 2. Adjust gain control until converter is switching from 11111111110 to 11111111111.

Table 4 summarizes the zero and gain adjustment procedure, and shows the proper input test voltages used in calibrating the DAS.

| Input<br>Voltage<br>Range | Adjust-<br>ment | Input<br>Voltage | Adjust input to point where converter is just on the verge of switching between the two codes shown.1 |

|---------------------------|-----------------|------------------|-------------------------------------------------------------------------------------------------------|

| 0.45 . 40\                | ZERO            | 1.22mV           | 00000000000<br>000000000001                                                                           |

| 0 to + 10V                | GAIN            | 9.9963V          | 111111111110<br>1111111111111                                                                         |

| . 57                      | ZERO -4.9988V   |                  | 00000000000<br>000000000001                                                                           |

| ± 5V                      | GAIN            | 4.9963V          | 111111111110<br>1111111111111                                                                         |

| . 10)/                    | ZERO            | - 9.9976V        | 00000000000<br>000000000001                                                                           |

| ± 10V                     | GAIN            | 9.9927V          | 111111111110<br>111111111111                                                                          |

<sup>&</sup>lt;sup>1</sup>Codes shown are natural binary for unipolar input ranges and offset binary for bipolar ranges

Table 4. Calibration Data

#### **POWER SUPPLY CONSIDERATION**

Power supplies used for the DAS should be selected for low noise operation. In particular they should be free of high frequency noise. Unstable output codes may result with noisy power sources. It is important to remember that 2.44mV is 1LSB for a 10 volt input.

Decoupling capacitors are recommended on all power supply pins located as close to the converter as possible. Suitable decoupling capacitors are  $10\mu\text{F}$  tantalum type in parallel with  $0.1\mu\text{F}$  disc ceramic type.

#### **GROUNDING CONSIDERATIONS**

The common at pin 5 is the ground reference point for the internal reference and is thus the high quality ground for the DAS. In order to achieve all of the high accuracy performance available from the DAS in an environment of high digital noise content, care should be taken when handling analog and digital grounds, as follows. Where analog and digital grounds are run separately on the PCB, these should be connected together at the package (pin 5). However, if the grounds are connected separately in the system for other reasons, then only the analog ground should be connected at the package to pin 5. If digital common contains high frequency noise beyond 200mV, this noise may feed through the converter, so that some caution will be required.

It is also important in the layout to carefully consider the placement of digital lines. It is recommended that digital lines not be run directly under the DAS. For optimum system performance, if space permits, a ground plane is advised under the DAS. This should be connected to a digital ground. Finally, in packaging the assembled DAS, the designer should also try to minimize any capacitive coupling that might occur at the top to the device.

# **ORDERING INFORMATION**

| Model<br>Number <sup>1</sup> | input<br>Range | System<br>Accuracy<br>(% FSR) | Full Scale<br>T.C.<br>(ppm/°C) | Temp.<br>Range  | MIL<br>Screening |

|------------------------------|----------------|-------------------------------|--------------------------------|-----------------|------------------|

| HS 94XXJ                     |                | ± 0.025                       | 50.0                           | 0°C to +70°C    | _                |

| HS 94XXK                     |                | ± 0.012                       | 20.0                           | 0°C to +70°C    | _                |

| HS 94XXS                     | SEE            | ± 0.025                       | 50.0                           | -55°C to +125°C | _                |

| HS 94XXT                     | NOTE 1         | ± 0.012                       | 25.0                           | -55°C to +125°C | -                |

| HS 94XXS/B                   |                | ± 0.025                       | 50.0                           | -55°C to +125°C | 883 Rev. C       |

| HS 94XXT/B                   |                | ± 0.012                       | 25.0                           | -55°C to +125°C | 883 Rev. C       |

NOTES:

| ١. | HS              | 94 <u>XX</u>   |

|----|-----------------|----------------|

|    | MODEL<br>SUFFIX | INPUT<br>RANGE |

|    | 10              | 0 to +10V      |

|    | 11              | ± 5V           |

|    | 12              | ± 10V          |

Add letter suffix as required above.

Specifications subject to change without notice.

**CAUTION:** ESD (Electro-Static Discharge) sensitive device. Permanent damage may occur when unconnected devices are subjected to high energy electro-static fields. Unused devices must be stored in conductive foam or shunts. Protective foam should be discharged to the destination socket before devices are removed. Devices should be handled at static safe workstations only. Unused digital inputs must be grounded or tied to the logic supply voltage. Unless otherwise noted, the voltage at any digital input should never exceed the supply voltage by more than 0.5 volts or go below -0.5 volts. If this condition cannot be maintained, limit input current on digital inputs by using series resistors or contact Hybrid Systems for technical assistance.