# **Signetics**

# 8X02A Control Store Sequencer

**Product Specification**

#### **Logic Products**

#### **FEATURES**

- 10-Bit Address Generator (1024 Microinstruction Addressability)

- Operating Frequency Exceeding 12 MHz

- Direct Branching Over Full Address Range

- Conditional Branching

- Subroutine Branching Capability

- 4-Level Stack Register File

- Loop Control Facility Using Stack

- Three-State Address Outputs

# PRODUCT DESCRIPTION

The Signetics 8X02A Control Store Sequencer generates addresses to access instructions from a microprogram memory (control store). This high-speed device provides an efficient means of controlling the flow through a microprogram

with a powerful set of sequencing functions. The 8X02A can directly address up to 1024 microinstructions; however, the total address space can be expanded by adding conventional paging techniques. Combined with memory, the 8X02A forms a powerful control section for CPU's, controllers, test equipment, and other microprogram-controlled systems

### 8X02A PACKAGE AND PIN DESIGNATIONS

| An [8] 39 MA; 8 - 13 (A <sub>0</sub> = LSB, A <sub>9</sub> = MSB).  As [9] MA; 8 - 13 (A <sub>0</sub> = LSB, A <sub>9</sub> = MSB).  As [10] 31 GND 7 GND Ground  Vcc [11] 39 MA; 14 - 21, B <sub>0</sub> - B <sub>9</sub> Branch address inputs: (B <sub>0</sub> = LSB, B <sub>9</sub> = MSB).  As [12] 29 MA; 23, 24  An; [13] 29 MA; 22 V <sub>CC</sub> Supply voltage.  An; [15] 38 MA; 25 CLK Clock input (positive edge used for all triggering).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | N PAC                                   | KAGE                |    |                                 |                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------|----|---------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Functions – see Table 1.  Functions – see T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A <sub>10</sub> 2<br>A <sub>2</sub> 3   | 39 WG<br>38 GNT     |    |                                 |                                                                                                                   |

| A <sub>1</sub> $\boxed{1}$ $\boxed{3}$ $\boxed{3}$ $\boxed{M}$ $\boxed{3}$ $\boxed{4}$ $\boxed{3}$ $\boxed{3}$ $\boxed{M}$ $\boxed{4}$ $\boxed{3}$ $\boxed{3}$ $\boxed{M}$ $\boxed{4}$ $\boxed{3}$ $\boxed{M}$ $\boxed{4}$ $\boxed{3}$ $\boxed{M}$ $\boxed{4}$ $\boxed{5}$ $\boxed{3}$ $\boxed{4}$ $\boxed{4}$ $\boxed{5}$ $\boxed{4}$ $\boxed{5}$ $\boxed{4}$ $\boxed{5}$ $\boxed{4}$ $\boxed{5}$ $\boxed{5}$ $\boxed{6}$ $$ |                                         | P                   | ,, |                                 |                                                                                                                   |

| An 3 MA, 8 - 13 (A <sub>0</sub> - K <sub>9</sub> Three-state address outputs used to specify microprogram address of the specify microprogram address in parts of the specify microprogram address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A12 8                                   |                     | 2  | ĒN                              | Enable three-state address outputs (A <sub>0</sub> - A <sub>9</sub> ); active-low input.                          |

| A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A13 8                                   | 33 MA1              | ,  |                                 | Three-state address outputs used to specify microprogram address ( $A_0 = LSB, \ A_9 = MSB$ ).                    |

| As 12 29 MA, 23, 24  Ats 13 28 MAs 23, 24  Ats 15 28 MAs 22 V <sub>CC</sub> Supply voltage.  Ats 15 28 MAs 25 CLK Clock input (positive edge used for all triggering).  At 17 29 P 26 TEST Active-high condition input used to determine conditional skip branches, subroutine calls, and loop termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A14 10                                  |                     | 7  | GND                             | Ground                                                                                                            |

| At 15 28 MA7 25 CLK Clock input (positive edge used for all triggering).  At 17 22 MA6 25 TEST Active-high condition input used to determine conditional skip branches, subroutine calls, and loop termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A6 12                                   | 29 MA4              |    | B <sub>0</sub> – B <sub>9</sub> | Branch address inputs: ( $B_0 = LSB$ , $B_9 = MSB$ ).                                                             |

| As IS Mas 25 CLK Clock input (positive edge used for all triggering).  Ary ID 29 P 26 TEST Active-high condition input used to determine conditional skip branches, subroutine calls, and loop termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |                     | 22 | $v_{cc}$                        | Supply voltage.                                                                                                   |

| As (iii 22) FEG2 branches, subroutine calls, and loop termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                     | 25 | CLK                             | Clock input (positive edge used for all triggering).                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A <sub>9</sub> 18<br>A <sub>18</sub> 19 | 23 SEL 2<br>22 REQ2 | 26 | TEST                            | Active-high condition input used to determine conditional skips branches, subroutine calls, and loop termination. |

December 4, 1985 7-115 853-0447 81495

8X02A

#### **FUNCTIONAL OPERATION**

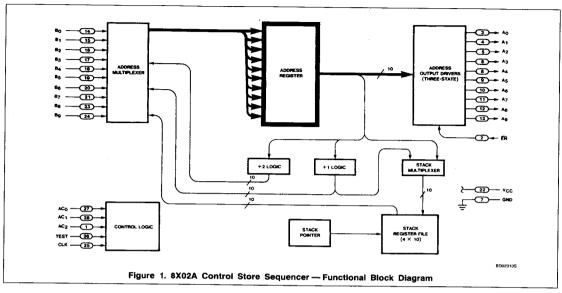

As shown in Figure 1, the data appearing on the address output pins  $(A_0 - A_0)$  is the contents of the 10-bit Address Register. On the rising edge of the clock input pulse (CLK), a new address is latched into the Address Register. This new address is supplied via the Address Multiplexer which selects one of five sources:

- Branch Address Input (B<sub>0</sub> B<sub>9</sub>)

- Current Address + 1

- Current Address + 2 (for the SKIP function)

- Stack Register File (most recent entry)

- All Zeroes (RESET)

The selection of the next address is determined by the "Address Control Function" specified by inputs  $AC_0 - AC_2$  and the TEST input. Table 1 defines the eight Address Control Functions.

The "Reset" (RST) Address Control Function unconditionally forces all Address Register bits to zero on the rising edge of CLK. Sequential microprogram flow is provided by the "Increment" (INC) function which unconditionally increments the Address Register by one for each clock cycle. The Address Register automatically wraps around from the highest address (all "1s") to the lowest address (all "0s").

As shown in Table 1, the TEST input is used to conditionally execute four of the eight Address Control Functions. If the TEST input is **low** (false), the Address Register is simply

incremented by one — (for the BLT function, the Stack Pointer is also decremented). If the TEST input is **high** (true), the sequencer executes one of the following:

- Skip (TSK) the Address Register is incremented by two.

- Branch (BRT) the Address Register is loaded from the Branch Address Inputs.

- Bronch to Cubacutine (DCD)

- Branch-to-Subroutine (BSR).

- Branch-to-Loop (BLT).

The Stack Register File holds up to four 10-bit addresses and operates in the Last-In/First-Out (LIFO) mode. A Stack Pointer keeps track of the next register of the Stack File to be written into; the pointer is incremented after each "push" and decremented after each "pop" — see Table 1. When branching to a subroutine (BSR), the return address (current address + 1) is "pushed" onto the stack and the branch address input is loaded into the Address Register. To return from a subroutine, the "POP" function pops the return address off the stack and loads it into the Address Register.

The "Push-for-Looping" (PLP) function may be specified in the first instruction of a loop to "push" the current address onto the stack: the Address Register is incremented. A "Branch-to-Loop" (BLT) function placed at the end of the loop "pops" the stack and conditionally branches to the top-of-loop address, depending on the TEST input. If the test for repeating the loop is satisfied (TEST input high), the sequencer causes a branch

back to the first instruction of the loop in which the top-of-loop address is "pushed" back onto the stack. If the test fails (TEST input low), the top-of-loop address is discarded, the stack pointer is decremented and the Address Register is incremented. A combination of subroutines and loops may be nested up to four levels deep.

In abnormal circumstances, the Stack Pointer will wraparound from the fourth to the first register of the Stack File and vice-versa. If the stack is full (four addresses currently stored), an additional "push" causes the first (oldest) entry to be overwritten — (the four most recent entries are always maintained). If the stack is empty, a "pop" will access the fourth register of the Stack File; however, the contents of this register may be unpredictable.

The three-state address outputs  $(A_0-A_9)$  are controlled by a common enable input  $(\overline{EN})$ . When the enable input is **high**, the output drivers are placed in the high-impedance state allowing alternative access to the microprogram memory. Other circuit functions are unaffected by  $\overline{EN}$ .

#### NOTE

To implement a RESET externally it is necessary to force all Address Control Inputs (AC $_0$  – AC $_2$ ) to the **high** state until at least one rising edge of CLK has occurred. If the AC inputs are supplied directly from the microprogram memory, a RESET may be accomplished by disabling the memory outputs. Pullup resistors should be provided to achieve the required high voltage level.

December 4, 1985

8X02A

Table 1. Address Control Functions

| MNEMONIC AND                                         | CONTROL LINES   |                 |                                 |   | NEVT ADDDESS                                                                    | OTACK OPERATION                                  | STACK                            |  |

|------------------------------------------------------|-----------------|-----------------|---------------------------------|---|---------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------|--|

| DESCRIPTION                                          | AC <sub>2</sub> | AC <sub>1</sub> | AC <sub>1</sub> AC <sub>0</sub> |   | NEXT ADDRESS                                                                    | STACK OPERATION                                  | POINTER                          |  |

| TSK - Test and skip                                  | 0               | 0               | 0                               | 0 | Current address + 1<br>Current address + 2                                      | No change<br>No change                           | No change<br>No change           |  |

| INC - Increment                                      | 0               | 0               | 1                               | Х | Current address + 1                                                             | No change                                        | No change                        |  |

| BLT - Branch to loop if test condition is true       | 0               | 1               | 0                               | 0 | Current address + 1<br>From stack register file                                 | POP (ignore data)<br>POP (read)                  | Decrement by 1<br>Decrement by 1 |  |

| POP - Pop stack (return from subroutine)             | 0               | 1               | 1                               | Х | From stack register file                                                        | POP (read)                                       | Decrement by 1                   |  |

| BSR - Branch to subroutine if test condition is true | 1 1             | 0               | 0                               | 0 | Current address + 1<br>Branch address inputs<br>B <sub>0</sub> - B <sub>9</sub> | No change<br>PUSH (write current<br>address + 1) | No change<br>Increment by 1      |  |

| PLP - Push for looping                               | 1               | 0               | 1                               | Х | Current address + 1                                                             | PUSH (write current address)                     | Increment by 1                   |  |

| BRT - Branch if test condition is true               | 1 1             | 1               | 0                               | 0 | Current address + 1<br>Branch address inputs<br>B <sub>0</sub> - B <sub>9</sub> | No change<br>No change                           | No change<br>No change           |  |

| RST - Reset address to zero                          | 1               | 1               | 1                               | X | All zeroes                                                                      | No change                                        | No change                        |  |

X = Don't Care

## **ABSOLUTE MAXIMUM RATINGS**

|      | PARAMETER                 | RATING      | UNIT |

|------|---------------------------|-------------|------|

| Vcc  | Power supply voltage      | +7          | Vdc  |

| ViN  | input voltage             | + 5.5       | Vdc  |

| Vo   | Off-state output voltage  | + 5.5       | Vdc  |

| TSTG | Storage temperature range | -65 to +150 | °C   |

# DC ELECTRICAL CHARACTERISTICS Conditions: Commercial – $V_{CC}$ = 5.0V (±5%), $0^{\circ}C \leqslant T_{A} \leqslant 70^{\circ}C$

| PARAMETER        | DESCRIPTION                                                                | TEST CONDITIONS                                 | Min | Typ <sup>1</sup> | Max  | UNIT |

|------------------|----------------------------------------------------------------------------|-------------------------------------------------|-----|------------------|------|------|

| V <sub>IH</sub>  | High level input voltage                                                   | V <sub>CC</sub> = Min                           | 2   |                  |      |      |

| V <sub>IL</sub>  | Low level input voltage                                                    | V <sub>CC</sub> = Min                           |     |                  | 0.8  | ]    |

| V <sub>IC</sub>  | Input clamp voltage                                                        | V <sub>CC</sub> = Min; 1 <sub>1</sub> = -18mA   |     |                  | -1.5 | _ v  |

| V <sub>OH</sub>  | High level output voltage                                                  | V <sub>CC</sub> = Min; I <sub>OH</sub> = -2.6mA | 2.4 | 3.4              |      |      |

| V <sub>OL</sub>  | Low level output voltage                                                   | V <sub>CC</sub> = Min; I <sub>OL</sub> = 8mA    |     | 0.42             | 0.5  |      |

| l <sub>l</sub>   | Input current at maximum input voltage                                     | V <sub>CC</sub> = Max; V <sub>I</sub> = 5.5V    |     | 1                | 100  | μΑ   |

| I <sub>IH</sub>  | High level input current:<br>AC <sub>2</sub> - AC <sub>0</sub> , TEST, CLK | V <sub>CC</sub> = Max; V <sub>IH</sub> = 2.7V   |     | < 0.1            | 40   | μА   |

|                  | B <sub>9</sub> – B <sub>0</sub> , EN                                       |                                                 |     | < 0.1            | 20   | 1    |

| I <sub>IL</sub>  | Low level input current:<br>AC <sub>2</sub> – AC <sub>0</sub> , TEST, CLK  | V <sub>CC</sub> = Max; V <sub>IL</sub> = 0.4V   |     | -24              | -800 | μΑ   |

|                  | B <sub>9</sub> – B <sub>0</sub> , EN                                       |                                                 |     | -12              | -400 | 1    |

| los              | Short circuit output current <sup>2</sup>                                  | V <sub>CC</sub> = Max                           | -15 | -60              | -100 | mA   |

| l <sub>OZH</sub> | High-Z state output current – high level                                   | V <sub>CC</sub> = Max; V <sub>OH</sub> = 2.7V   |     |                  | 20   | μΑ   |

| lozL             | High-Z state output current<br>low level                                   | V <sub>CC</sub> = Max; V <sub>OL</sub> = 0.4V   |     |                  | -20  | μΑ   |

| Icc              | Supply current                                                             | V <sub>CC</sub> = Max                           |     | 170              | 250  | mA   |

NOTES:

7-117

December 4, 1985

<sup>1.</sup> Typical limits are:  $V_{CC}$  = 5.0V and  $T_A$  = 25°C. 2. For purposes of testing, not more than one output should be shorted at a time.

8X02A

AC ELECTRICAL CHARACTERISTICS Conditions: Commercial –  $V_{CC}$  = 5.0V (±5%), 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C Loading – See Test Loading Circuit

|                             | PARAMETERS <sup>1</sup>               | REFER                             |                                   | LIMITS4 |                  |     |      |

|-----------------------------|---------------------------------------|-----------------------------------|-----------------------------------|---------|------------------|-----|------|

|                             | FARAMETERS                            | From                              | То                                | Min     | Typ <sup>2</sup> | Max | UNIT |

| Pulse w                     |                                       |                                   |                                   |         |                  |     |      |

| t <sub>CW</sub>             | Clock cycle time                      | 1 CLK                             | 1 CLK                             | 80      |                  |     | ns   |

| tpwH                        | Clock high                            | ↑ CLK                             | ↓ CLK                             | 35      | 24               |     | ns   |

| t <sub>PWL</sub>            | Clock low                             | ↓ CLK                             | 1 CLK                             | 15      | 9                |     | ns   |

| Propaga<br>t <sub>PLZ</sub> | ntion delay:<br>Low to high-Z         | ↑ <del>E</del> N                  | A <sub>0</sub> – A <sub>9</sub>   |         | 14               | 20  | ns   |

| t <sub>PHZ</sub>            | High to high-Z                        | ↑EN                               | A <sub>0</sub> – A <sub>9</sub>   |         | 35               | 42  | ns   |

| tezL                        | High-Z to low                         | ↓EN                               | A <sub>0</sub> – A <sub>9</sub>   |         | 10               | 20  | ns   |

| t <sub>PZH</sub>            | High-Z to high                        | ↓EN                               | A <sub>0</sub> - A <sub>9</sub>   |         | 20               | 30  | ns   |

| t <sub>PHL</sub>            | High to low                           | 1 CLK                             | ↓ A <sub>0</sub> – A <sub>9</sub> |         | 25               | 45  | ns   |

| tplH                        | Low to high                           | ↑ CLK                             | 1 A <sub>0</sub> – A <sub>9</sub> |         | 25               | 45  | ns   |

| t <sub>HA</sub>             | Address output hold time <sup>3</sup> | 1 CLK                             | A <sub>0</sub> - A <sub>9</sub>   | 13      |                  |     | ns   |

| Set-up/h<br>t <sub>SF</sub> | nold times:<br>Function set-up time   | AC <sub>0</sub> – AC <sub>2</sub> | ↑ CLK                             | 20      | 18               |     | ns   |

| t <sub>SK</sub>             | Branch set-up time                    | B <sub>0</sub> – B <sub>9</sub>   | ↑ CLK                             | 15      | 7                |     | ns   |

| t <sub>SI</sub>             | Test set-up time                      | TEST                              | 1 CLK                             | 20      | 15               |     | ns   |

| t <sub>HF</sub>             | Function hold time                    | 1 CLK                             | AC <sub>0</sub> - AC <sub>2</sub> | 20      | 2                |     | ns   |

| t <sub>HK</sub>             | Branch hold time                      | 1 CLK                             | B <sub>0</sub> - B <sub>9</sub>   | 15      | 9                |     | ns   |

| t <sub>HI</sub>             | Test hold time                        | 1 CLK                             | TEST                              | 12      | -2               |     | ns   |

#### NOTES:

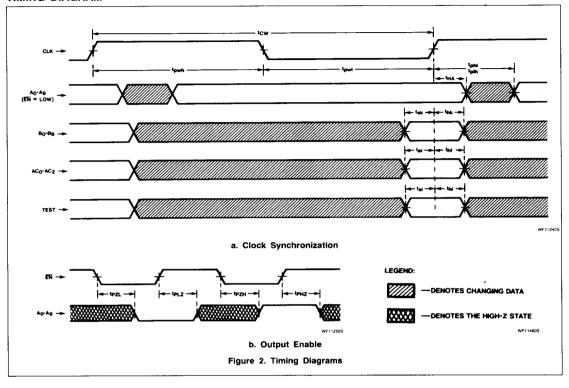

<sup>1.</sup> Parameter definitions are illustrated in the Timing Diagrams - See Figure 2.

<sup>2.</sup> Typical limits are:  $V_{CC} = 5.0V$  and  $T_A = 25^{\circ}C$ .

t<sub>HA</sub> is the minimum time the current address outputs remain stable before changing. This delay may be used to provide some of the hold times required for the AC, B, and TEST inputs, if these inputs are determined by the microprogram memory addressed by the 8X02A.

<sup>4.</sup> This data supercedes the November, 1980 edition of this data sheet.

8X02A

#### TIMING DIAGRAM

8X02A

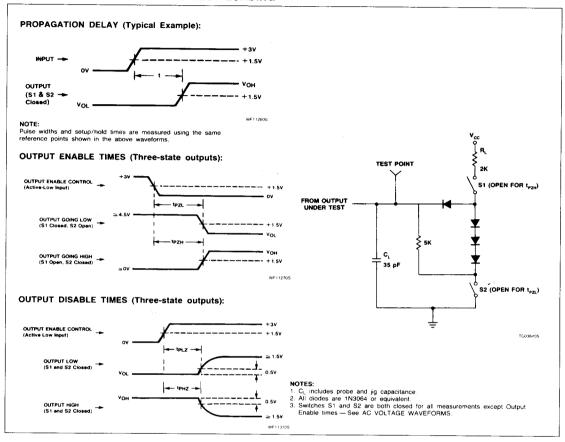

# AC VOLTAGE WAVEFORMS AND TEST LOADING

8X02A

#### **APPLICATION**

# **FUNCTIONAL DESCRIPTION**

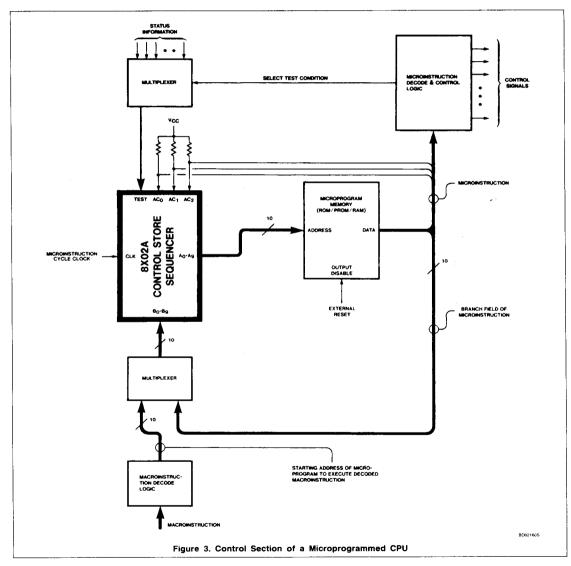

Figure 3 shows a typical configuration of an 8X02A-based control section in a CPU application. Microinstructions read from the memory are used to produce control signals for

the CPU and to determine the next microinstruction via the 8X02A Address Control inputs (AC $_0$  – AC $_2$ ). In the case of a conditional branch or skip, the status condition applied to the 8X02A TEST input is selected according to the microinstruction. In a branch-type microinstruction, a branch field typically supplies the 8X02A Branch Address inputs (B $_0$  – B $_9$ ). (In non-branching instructions, this field may

contain other CPU control information.) When a macroinstruction is presented to the CPU, the starting address of the microprogram routine which executes the macroinstruction is presented to the Branch Address inputs. Similar configurations may be used for other applications in which the Branch Address inputs are typically supplied directly from the microprogram memory.

December 4, 1985

7-121